Verilog is also known as VHDL and it stands for Verilog Hardware Description Language. It allows users to design digital circuits to study 'how a circuit behaves at the register transfer level'. In Australia, you will find numerous Verilog courses such as Advanced Digital Design, Digital Systems and Microprocessors, etc. During these studies, you are required to prepare assignments for topics like blocking and non-blocking, coding for the circuit, testbench development, use of signed data type, and more. Struggling to write a Verilog assignment? Avail Verilog assignment help from our experts!

Implementing the design requires the understanding and knowledge of various designs used at multiple levels of abstractions. Some of them are described below by our Verilog assignment writing expert. So, let's read them.

Register Transfer Level - The provisions describing the features of a circuit by using various transferring and operational data between logical operations and hardware registers. In the field of digital circuit design, the register transfer level is explained as a design abstraction that develops a synchronous digital circuit.

Behavioural Level - This level specifies a system that is involved with concurrent algorithms. Each instruction is performed sequentially which indicates that the main functions, elements, tasks, and blocks are executed in a sequence manner. Finding difficulties in writing Verilog assignments? Avail our Verilog assignment services today!

Gate Level - Verilog is built with primitives such as gates, switches, and transmission gates. Basically, these are used to design RTL Coding but also used in modelling the FPGA/ ASIC cells. After this, such cells are used for SDF Simulation which is also called Gate Level Simulation.

If you are a student and facing issues in writing assignments for implementing the design in Verilog, then our Verilog assignment writing experts will assist you.

The study of Verilog or VHDL is broad including numerous topics such as design methodology, sequential logic design, combinational logic design, logic design with Verilog, and many more. In this section, we have explained these topics in detail by the help of our Verilog assignment experts.

Design Methodology: The use of multimedia applications on devices like mobile, IPad, IPod, laptop, etc. has increased to an extent level. The silicon intelligent properties SOC chips functionalities have become difficult and complicated to design. The traditional form of designing a digital circuit uses a register transfer level that focuses on the register's time control, data path composition, and combinational circuit function. Thus, it leads to debug and difficulties in designing because of a huge synchronous signal and control. Therefore, to solve the above problems, a new digital system design methodology is introduced that is also called data-oriented methodology.

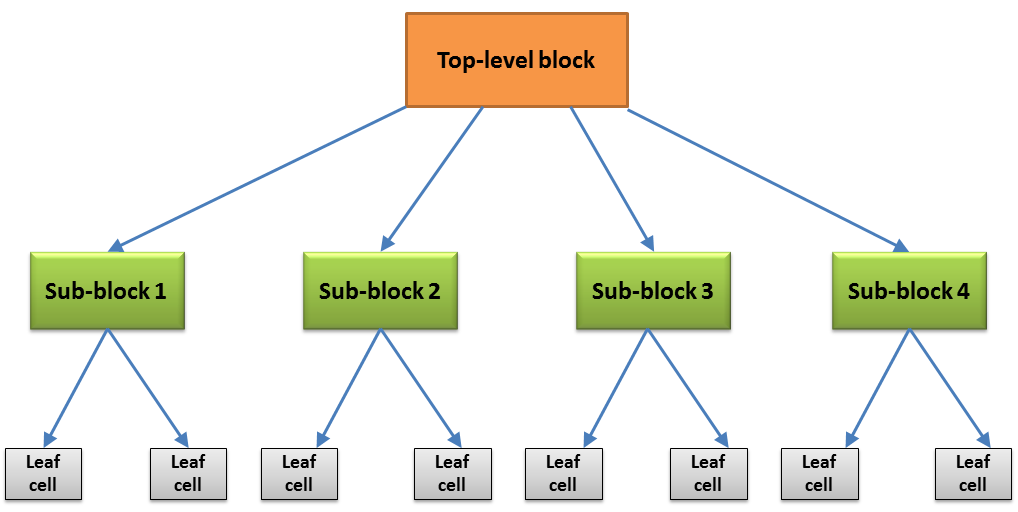

Top-down design methodology: In this methodology, the top-level block is defined and determines the sub-blocks that are important in building a top-level block. When using this for writing the assignments, our Verilog experts subdivide the sub-blocks until they find the leaf cell. Here's what a top-block looks like:

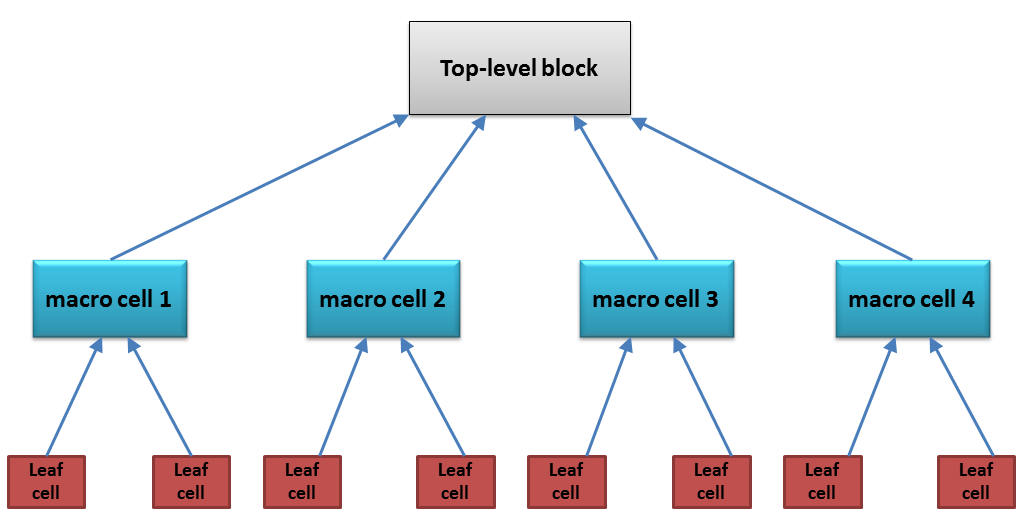

Bottom-up design methodology: In this design methodology, you first need to find out the building blocks and use them to build bigger cells. Now, the built cells are utilised for higher-level blocks until they build the top-level block design. For example -

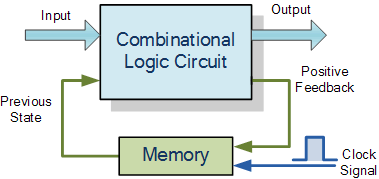

Sequential Logic Circuits: Sequential logic circuit comes with an in-built memory. It means that sequential logic circuits can take their previous and present input state into account. It can be also said that the output state of this circuit is a function including the following states; present output, past output, and/or past output. Our Verilog assignment writing experts can draft you high-quality assignments based on these circuits.

The sequential logic circuit can be classified into three main categories such as:

Combinational Logic Circuits: The combinational logic circuit does not have feedback or changes in the signals. The output that is dependent on the input of the combination is missing from such circuits. Therefore, it can be said the combinational circuit does not have a memory.

In the combinational logic circuit, there are three main ways to stipulate its functions such as Boolean algebra, Logic Diagram, and Truth Table. To gain further knowledge of the combinational logic circuit or its functions, avail our Verilog assignment services.

Dealing with Verilog assignments can be difficult to tackle. Recently, our Verilog assignment help expert had written an assignment, "ELEC4720 Programmable Logic Design". It is a group assessment consisting of 2 students. Under this assessment, you are required to cover two different parts including the following tasks.

The report must describe the instruction circuit diagrams, set architecture, and required logic derivations whereas the source code should include the .sv implementation of the CPU hardware and related test circuit on the DE2 board.

In case, if you find any sort of difficulty in writing with ELEC4720 Programmable Logic Design assessments, just contact our programming assignment experts. They will help you in completing the task accurately as per the instructions and guidelines are given by the professor.

Want to avail authentic assignment help in Australia? Just get in touch with our teams at Online Assignment Expert! We also cover subjects like management, science, engineering, programming, mathematics, economics, accounts, finance, etc. Hence, no matter what course you are enrolled in, just contact us and hire the world's best academic writers at pocket-friendly prices.

In addition to these, we have a team of assignment writing experts assisting Australian students in terms of understanding, researching, writing, proofreading, editing, and quality check of their assignment. Thus, if you are pursuing Verilog courses and have got stuck in writing the assignments, feel free to avail Verilog assignment help from us and get an accurate and complete paper before the submission date.

Get 24x7 instant assistance whenever you need.

Get affordable prices for your every assignment.

Assure you to deliver the assignment before the deadline

Get Plagiarism and AI content free Assignment

Get direct communication with experts immediately.

Secure Your Assignments

Just $10

Pay the rest on delivery*

It's Time To Find The Right Expert to Prepare Your Assignment!

Do not let assignment submission deadlines stress you out. Explore our professional assignment writing services with competitive rates today!

Secure Your Assignment!